发布于:2024-11-17 作者:😃思研

一、ESD概念,原理分析

1.ESD的定义

ESD,即静电释放。在ⅠC中ESD指ESD保护器件和ESD测试

2.ESD器件定义

在电路中,直接连接到PAD的器件有被"静电放电"冲击的风险。所以工艺厂提供了可以抗ESD冲击的器件,称为ESD器件

3.ESD处理定义

电路中标注的ESD处理就是指,在版图中要对应的器件进行ESD保护处理,即采用特殊画法,称为ESD画法,使器件具有和ESD器件一样的抗ESD特性。使这个器件可以抗住ESD测试的电压,且正常工作时不影响电路性能

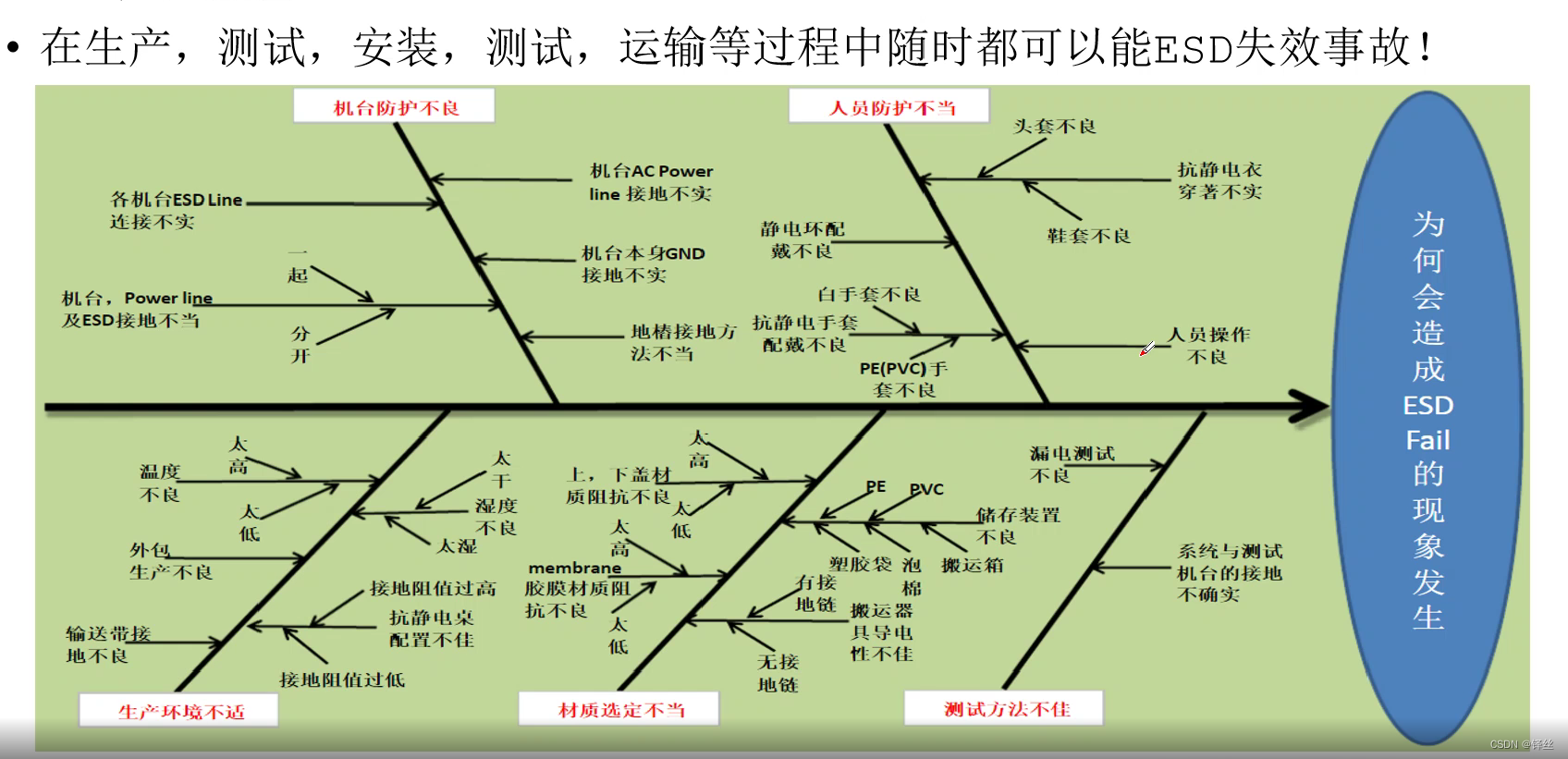

4.ESD产生原因

5.常见的ESD模型

①人体放电模型,HBM

②机器放电模型,MM

③元件充电模型,CDM

④电场感应模型,FIM

主要测①③,①最常见,也是对ⅠC损坏率最高

6.行业标准ESD测试模型

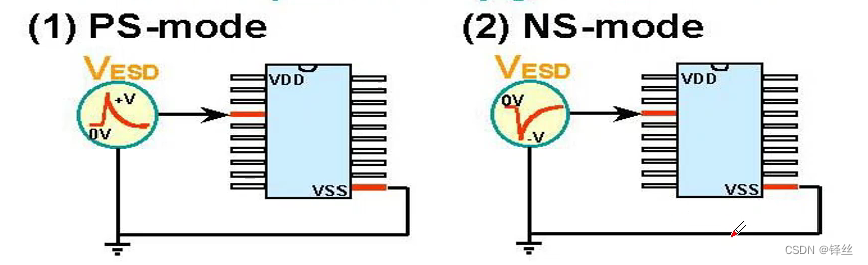

ESD在同一测试PⅠN上,分为打正电(p代表打正)和打负电(N代表打负),打正电的时候输入是正电压,打负的时候输入为负电压

①PIN to Vss

PS:所有IO PIN(电源,地PIN以外的都是IO),向Vss PIN打正电

NS:所有I0 PIN向Vss PIN打负

②PIN to VDD

PD:所有IO PIN向VDD PIN打正电

ND:所有IO PIN向VDD PⅠN打负电

③PIN to PIN

IO PIN打正,负到IO PIN,不包含电源,地PIN

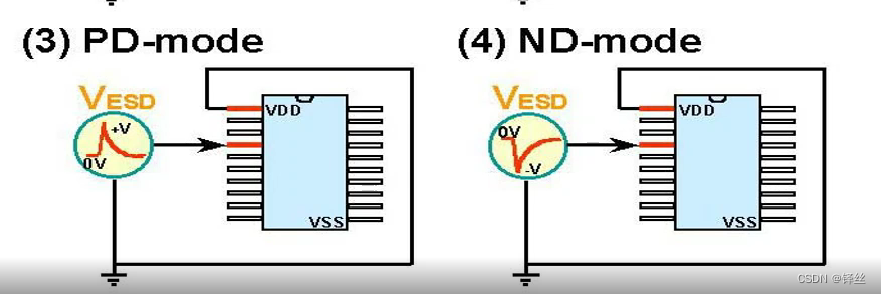

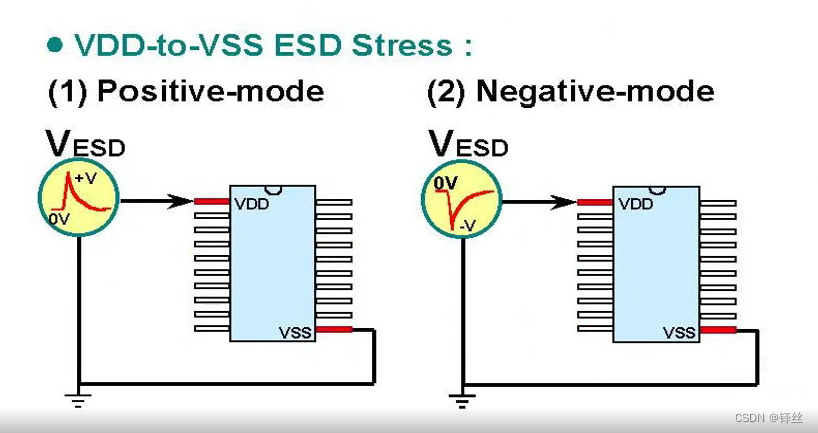

④VDD to VSS

电源PIN打正,负到VSS,等同于地PIN打正,负到VDD

⑤VIN和VIP

差分对

7.ESD保护器件,电路简介

常用的ESD保护器件有电阻,二极管,双极性晶体管,Mos管,可控硅等,由于MOS管和cmos工艺兼容性好,因此经常采用MOS管构造保护电路。

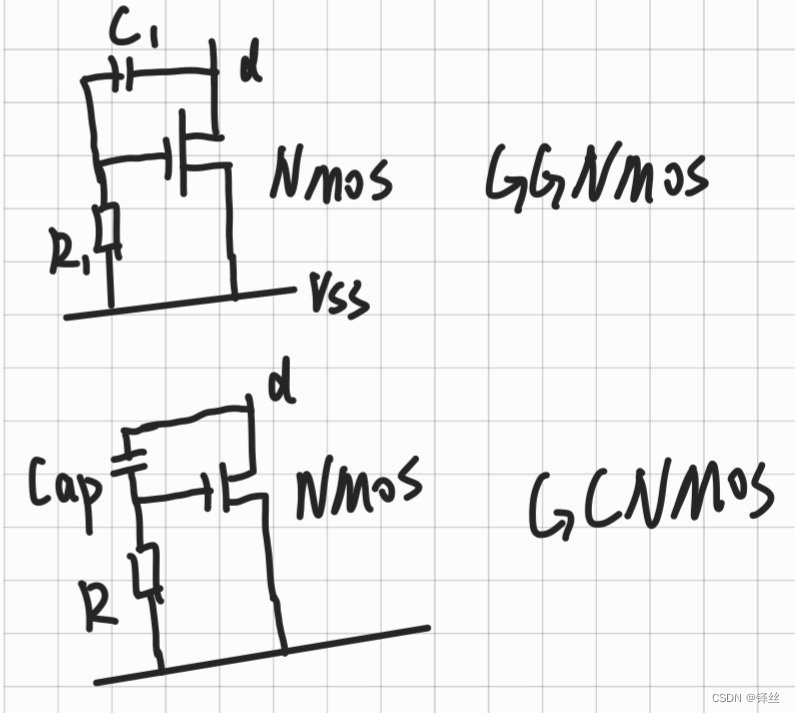

Cmos工艺条件下的MOS管有一个横向寄生的n-p-n晶体管,这个寄生的晶体管开启时能迅速泻放ESD电流。利用这一现象可在较小面积内设计出较高ESD耐压值的保护电路。其中最典型的是栅级接地电位的NMos和GCNMos

图

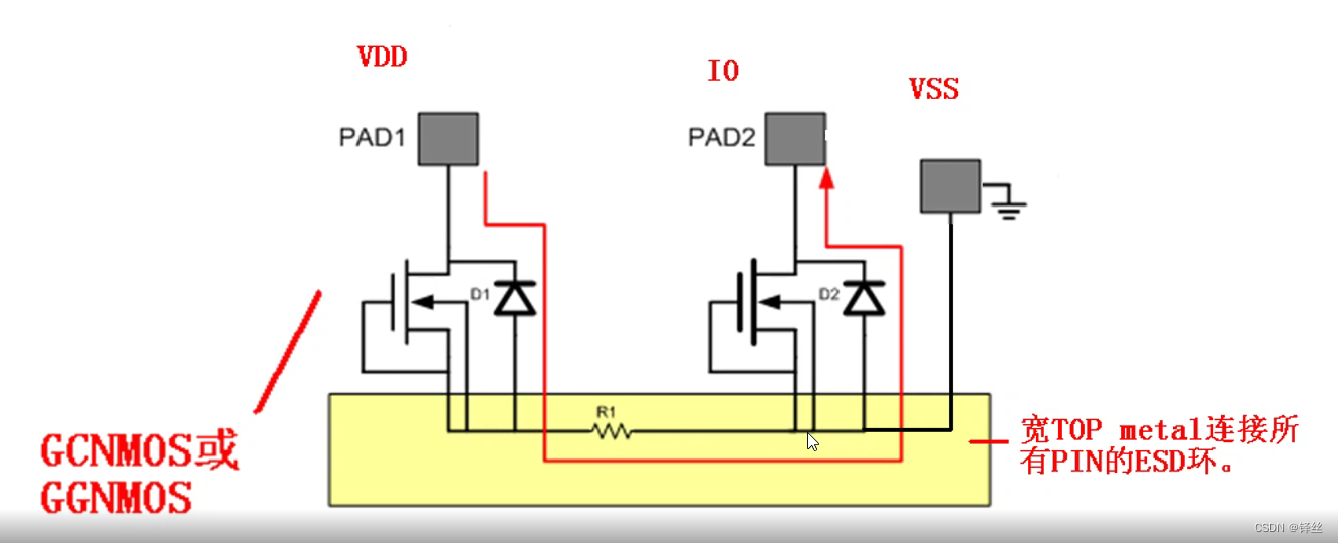

8.ESD电路通路模型

任何PIN和PIN,和VDD,VSS之间都要有电流通路。这个通路基本连接所有的PIN,简称ESD环

一般PⅠN到VDD都是ESD MOS管—ESD Metal环—ESD Mos管,这样的通路实现的

二、版图的ESD失效分析

1.ESD版图失效类型

ESD失效的原因是因为大电流和大电压,电流可以烧毁MOS管,电压可以把栅氧打坏。对版图来说,大体分为2种:

①ESD保护器件失效

ESD器件是ESD发生时,限制电压提高,泻放电流的第一通路,所以也是受电压、电流冲击最大的地方。所以ESD器件本身的版图设计要满足ESD测试,实际应用的情况需求

②内部电路失效

在ESD发生时,如果ESD保护器件没有及时起作用,那么PAD处的电压就会传导到芯片内部,如果PAD连接器件gate,就可能打坏这个器件。如果连接到D、S端,可能DG击穿,也可能DS击穿,甚至可能引发IO到地的Latch up(这种情况不易发生,需要IO PAD的特殊应用环境),导致器件烧毁

2.ESD保护器件NMos管(GGNMos,GCNMos)工作原理和失效分析

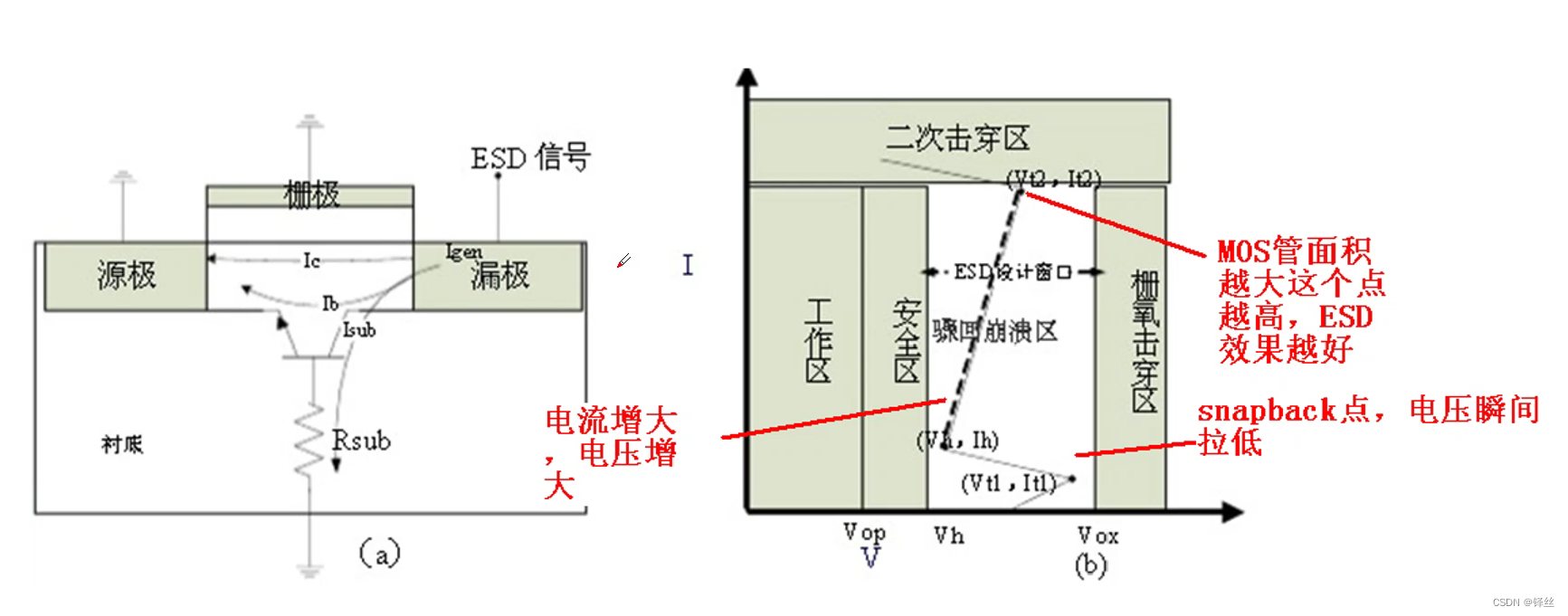

正常工作情况下,NMOS横向晶体管不会导通。当ESD发生时,漏极和衬底的耗尽区将发生雪崩击穿,并伴随电子空穴对的产生,一部分产生的空穴被源极吸收,其余的流过衬底。由于衬底电阻Rsub的存在,使衬底电压提高。当衬底和源之间的pn结正偏时,电子就从源发射进入衬底。寄生三级管NPN开启(snapback点,三极管开启后电流通路就变成了低阻通路,虽然电流变大,但是电压还是瞬间拉低)这些电子在源漏之间电场的作用下,被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,最终使NMos晶体管发生二次击穿

若无限流措施,大电流通过截面很小的局部热斑,将产生大量热量,而单位时间能散发出的热量是有限的,由此,引起热斑温度急剧上升,直至达到半导体材料的熔点,使材料熔化,产生熔融孔,造成晶体管永久失效

三、版图的ESD管可靠性设计

1.mos管ESD器件剖面图,工作特性I、V曲线图:

①d面积大(散热好)

②SAB:a.防止LDD击穿;b.增加阻抗

③cont孔to poly space↗

④PESD注入↗

2. 5v mos管和5v普通mos管的区别:

3.Mos管ESD器件的特殊版图画法,为了实现:

①增加电阻,达到整流的作用,也就是说电流会更加均匀的通过沟道

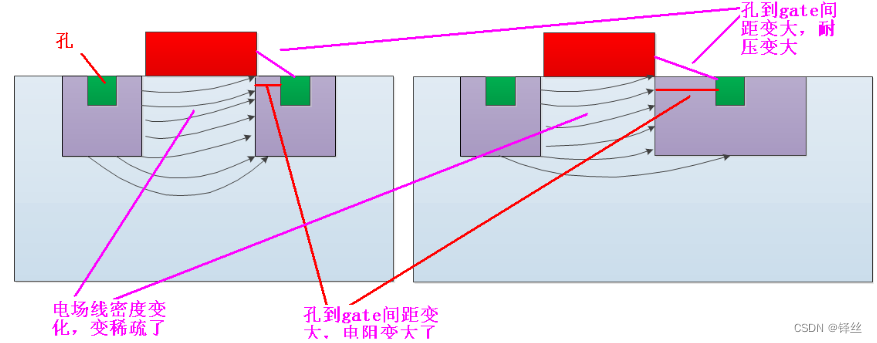

②加宽D端到gate间距,间距变大,增加了DG、DS间的耐压,同时增加了散热面积,分散了电场线密度,相同电流下减弱了热载子效应,抬高了烧毁器件需要的电流大小,进而抬高了ESD电压

4.ESD环路Metal电阻对ESD性能的影响:

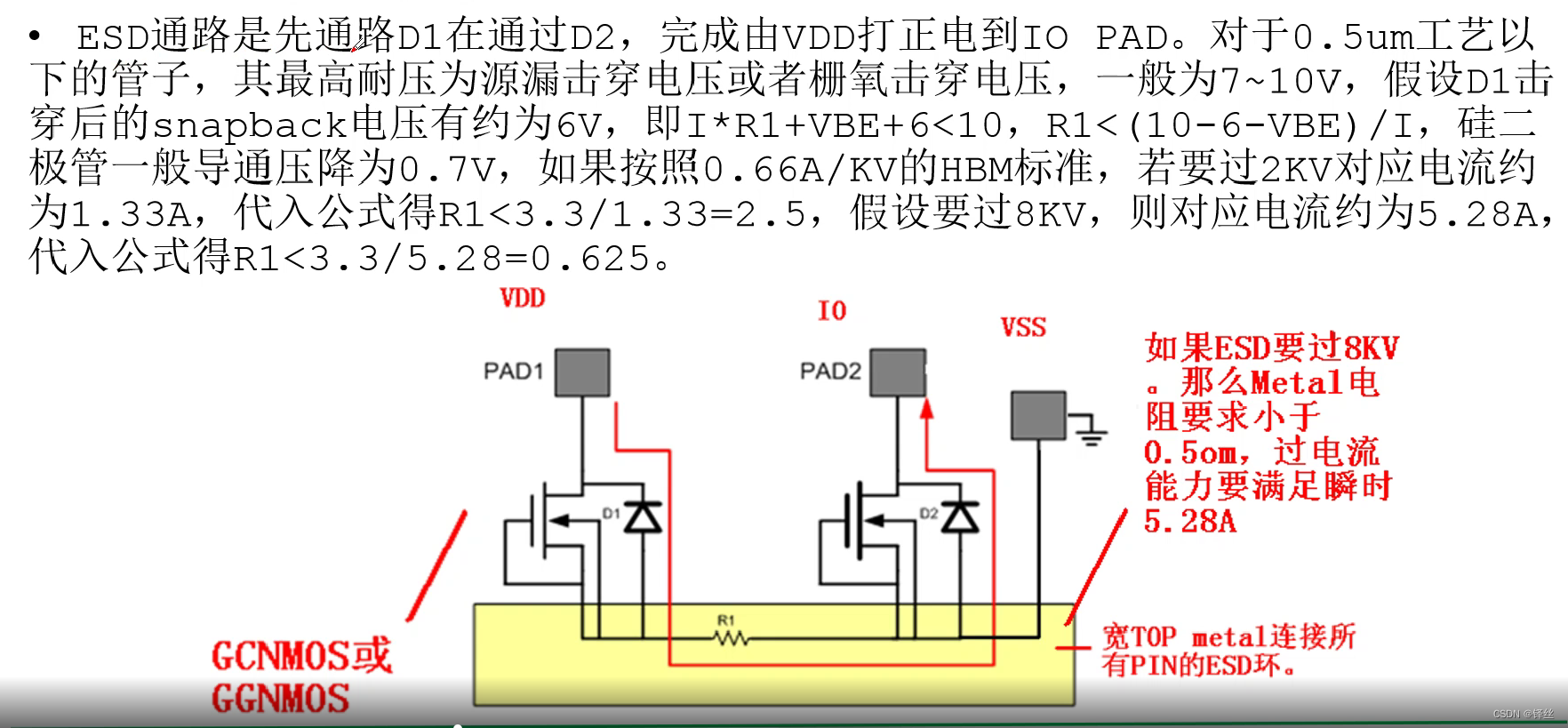

ESD通路是先通路D1在通过D2,完成由VDD打正电到IO PAD。对于0.5um工艺以下的管子,其最高耐压为源漏击穿电压或栅氧击穿电压,一般为7~10V,假设D1击穿后的snapback电压约有6Ⅴ,即I*R1+VBE+6<10,R1<(10-6-VBE)/Ⅰ,硅二极管一般导通压降为0.7V,如果按照0.66A/KV的HBM标准,若要过2kV对应电流约为1.33A,代入公式得R1<3.3/1.33=2.5,假设要过8kv,则对应电流约为5.28A,代入公式得R1<3.3/5.28=0.625

四、版图内部器件可靠性设计

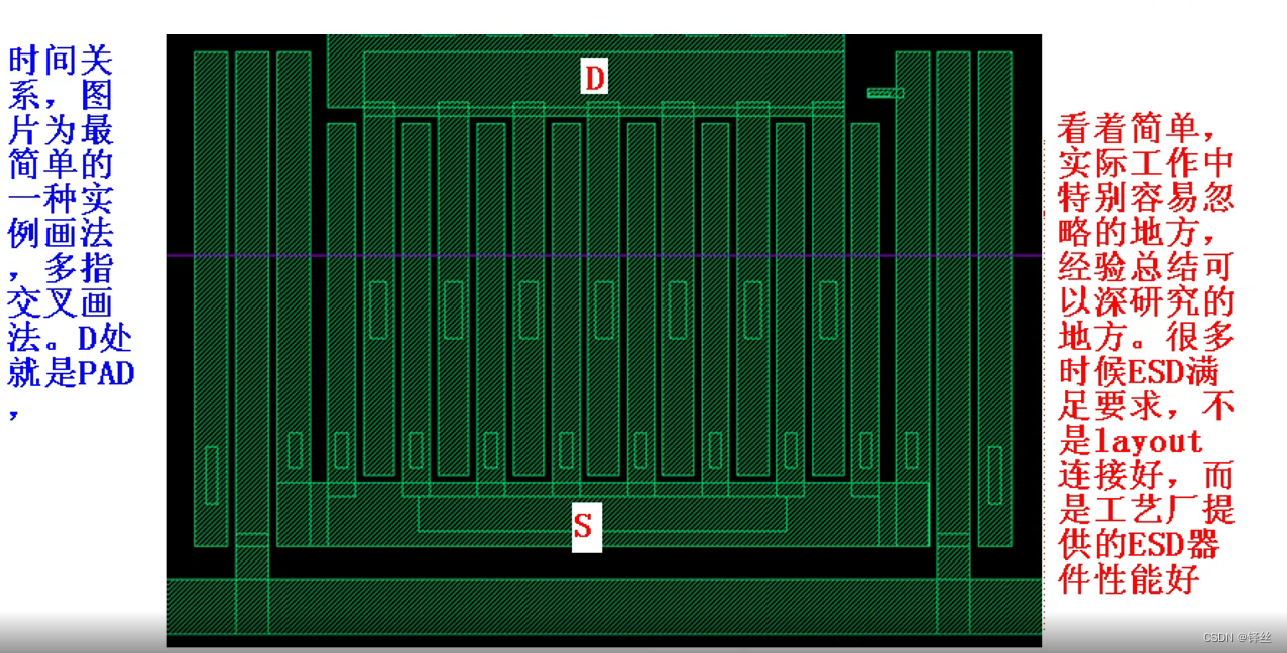

1.对于ESD器件来说,我们所做的改动都是为了电流的均匀性。∴大家要注意连接ESD的metal的寄生电阻不同是否会造成ESD器件的不均匀开启。现在的工艺,己经基本不用layout自己画ESD器件了,或只是照着工厂的ESD器件进行改动。对版图来说,metal画法才是考验功力的地方。

2.内部连接到PAD的器件ESD可靠性处理方法:

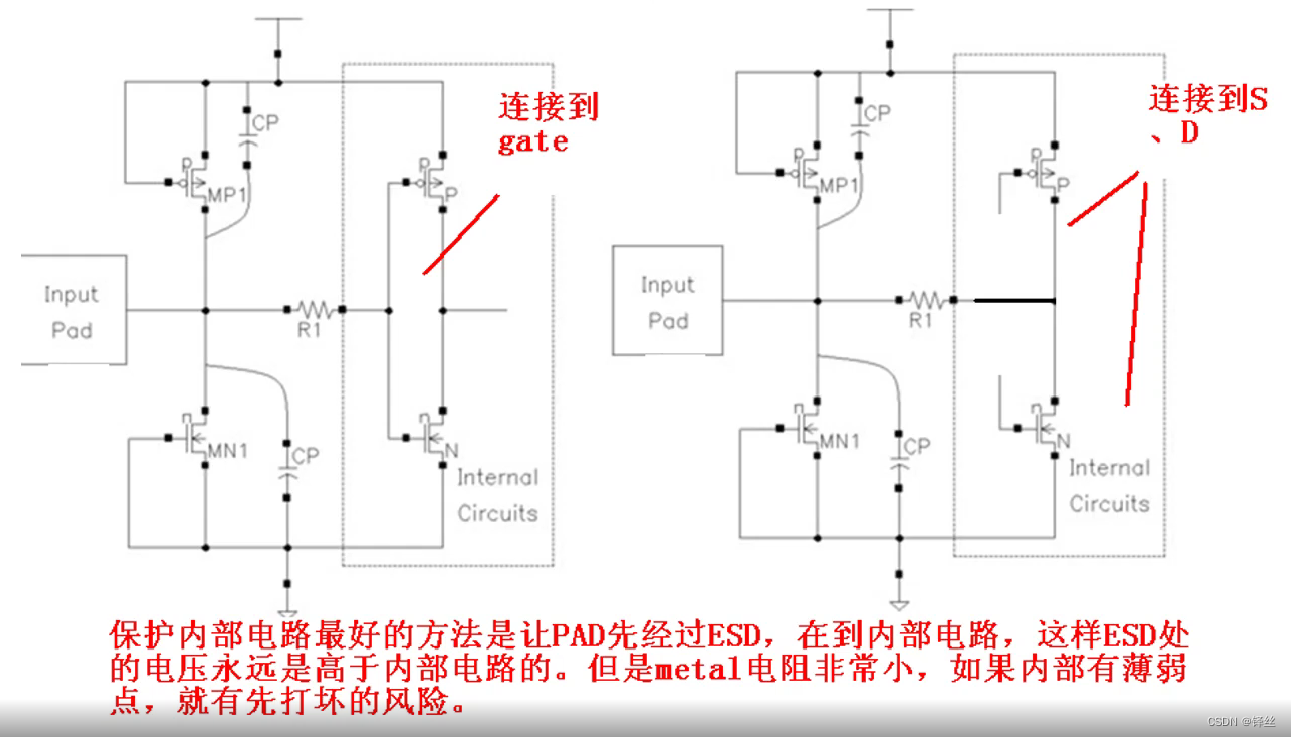

PAD连接到内部就2种情况,连接到gate和连接到S、D端

⑴PAD连接到gate的器件

在gate前加一个ESD电阻。此电阻在ESD的时候分压。让内部器件gate电压小于PAD处电压。同时可防止大电流浪涌冲击到内部。

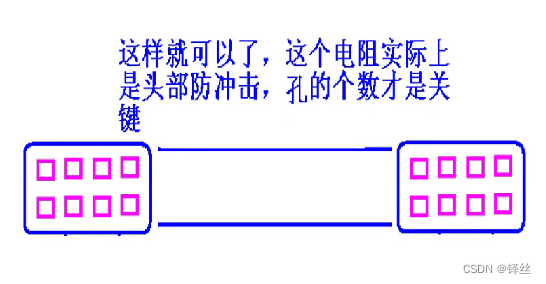

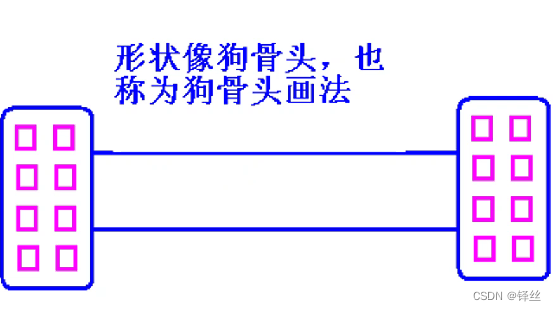

ESD电阻是指电阻头的孔的个数做处理加多到8个以上的电阻

⑵PAD连接内部SD器件

①采用和ESD器件一样的画法,优:ESD性能高,缺点是费面积,可能制约芯片性能

②在源漏端前面加ESD电阻,优点是省面积,缺点是限流、分压。对性能有一定影响,同时电阻值大小不好确定,在量产时有良率风险

③对接PAD的mos采用特殊处理,在ESD性能和面积上进行折中处理。在PAD处理有ESD情况下,内部器件大部分是不需做的和ESD器件拥有一样抗ESD性能的,只要提高到ESD器件先触发就可以了,∵ESD器件触发后就会快速拉低电压

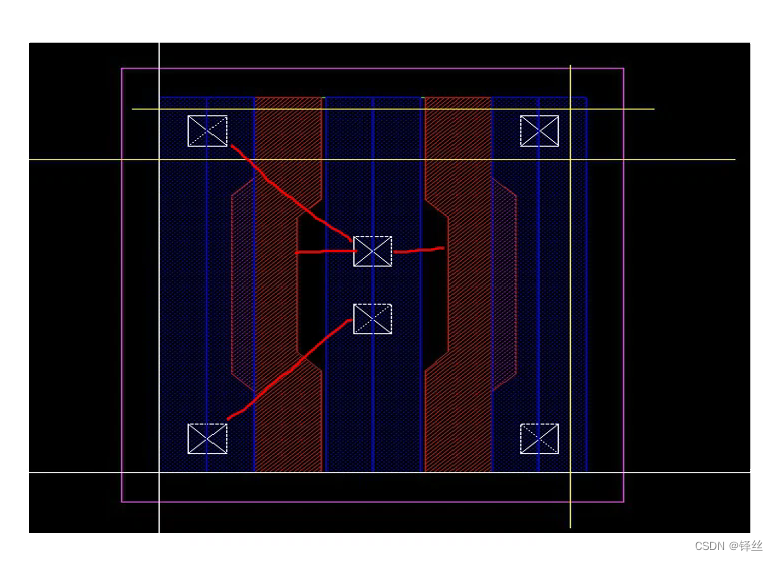

3.曲栅(弯栅)增加了栅极的宽度,使栅极捏死紧密,可轻易容纳分布式背栅接触孔,栅极135度弯曲不易发生局部雪崩击穿,源和漏接触孔对角放置增加源、漏间距,电阻变大,整流作用,改善器件稳定性

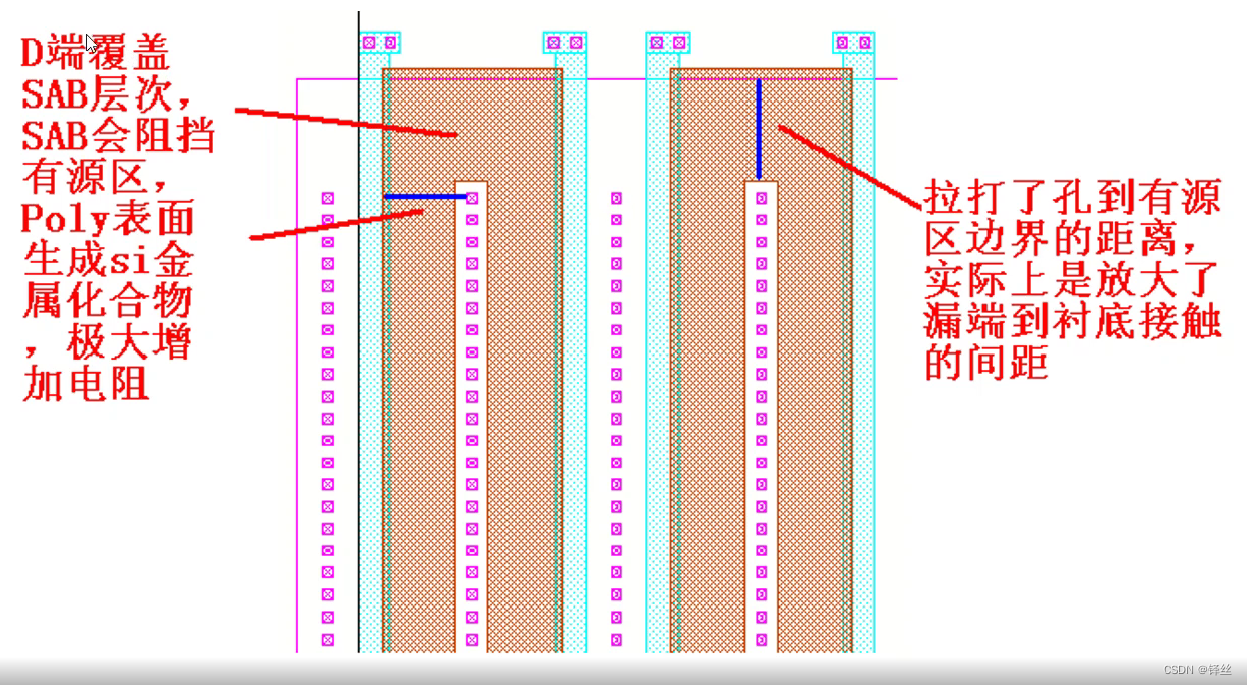

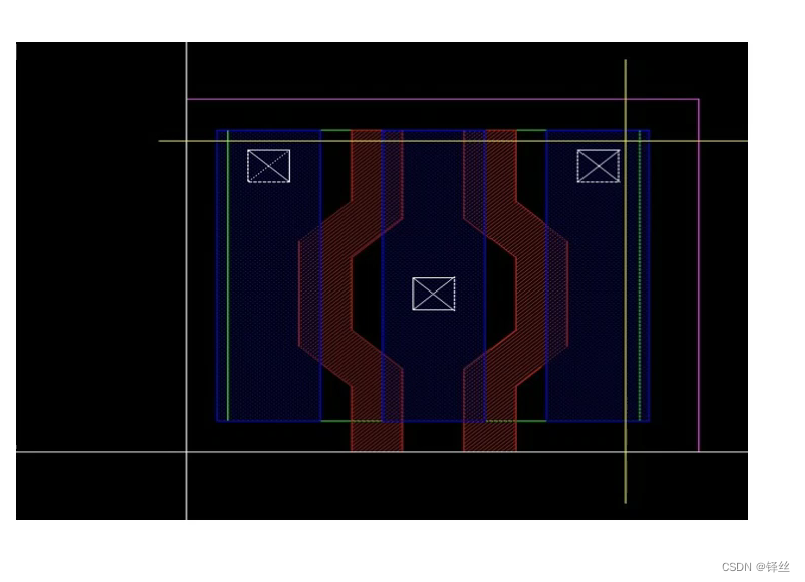

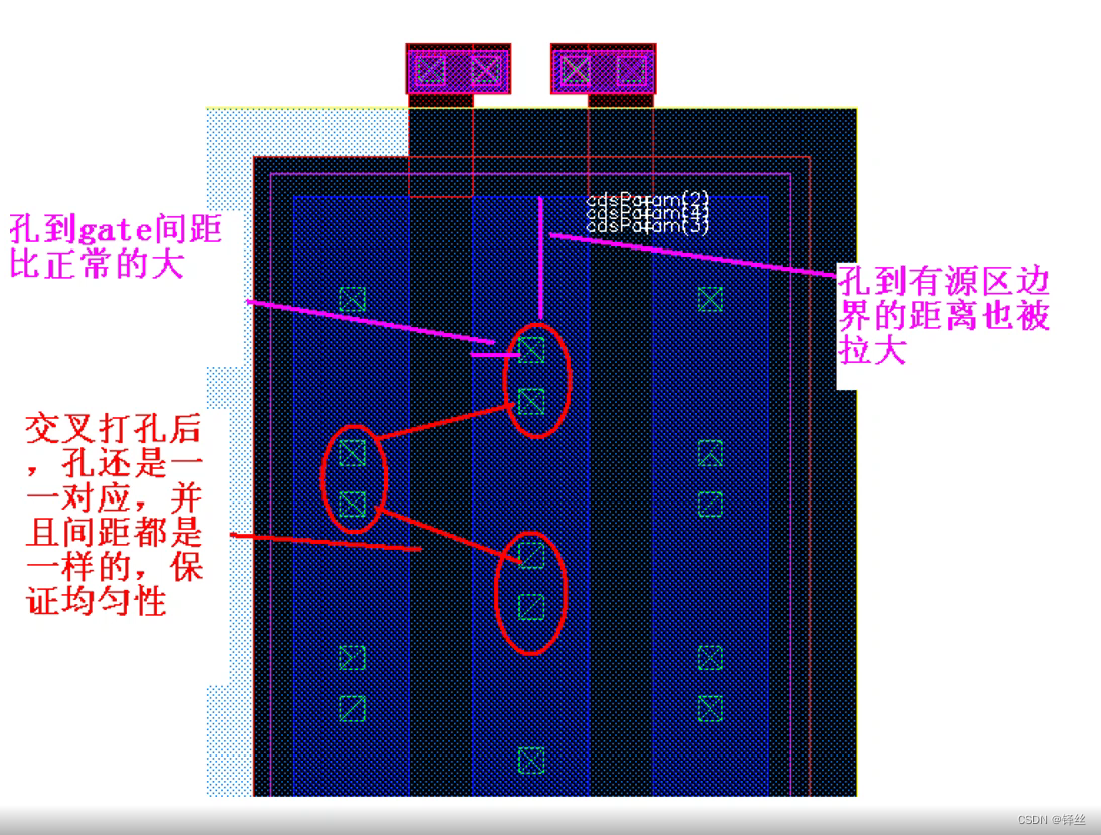

4.去孔,交叉打孔

交叉打孔也相当于增加孔到gate的平均距离,增加有源区电阻

图

去孔,减少了孔的个数,增加通路电阻,可限流

直接拉开孔到gate的间距,一般来说,根据管子面积大小来确定拉开间距是多少,管子总面积越大,拉开间距越小。∵管子大了后,过电流能力增加

原文链接:https://blog.csdn.net/weixin_52567455/article/details/129766489