作者:😃思研

2026-01-04

一:应用背景

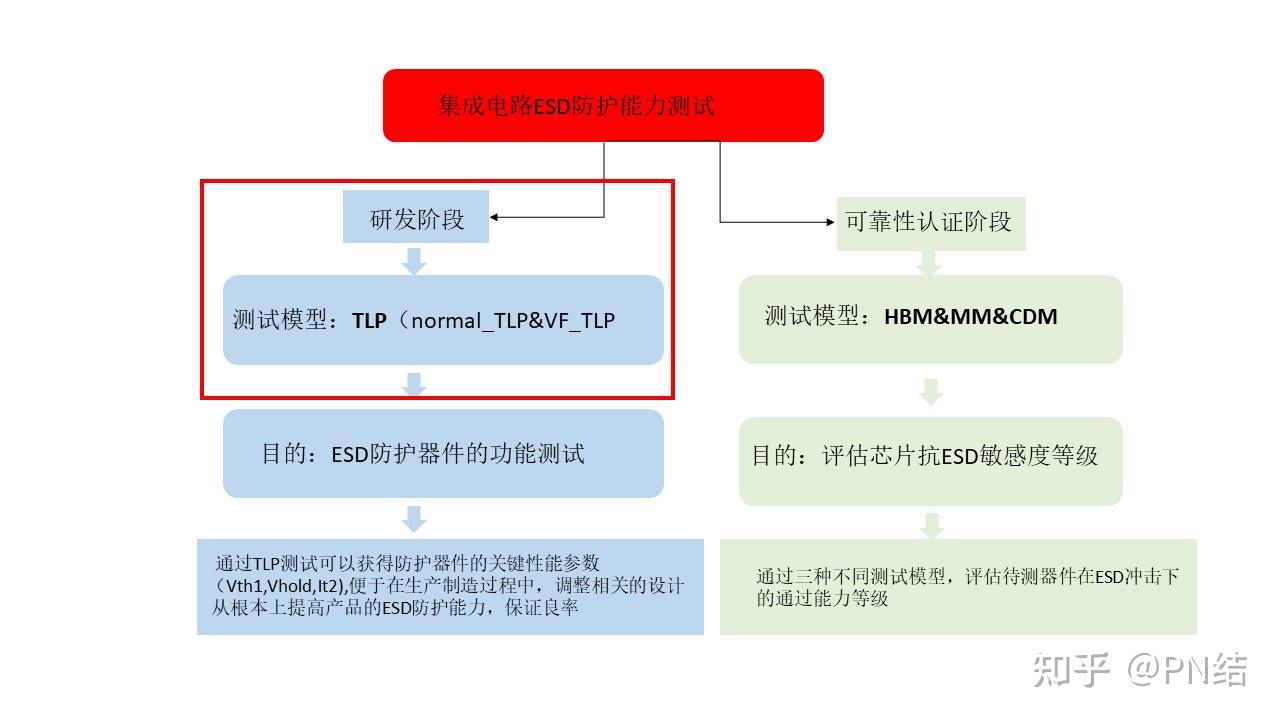

静电放电始终是 IC 可靠性和生产中的一个关注领域。要设计有效的 ESD 钳位了解钳位在 ESD 事件期间如何开启和运行至关重要。测得的保护器件 IV 特性有助于了解构成 ESD 稳健性或保护弱点的物理机制。这反过来又允许对保护进行详细优化。

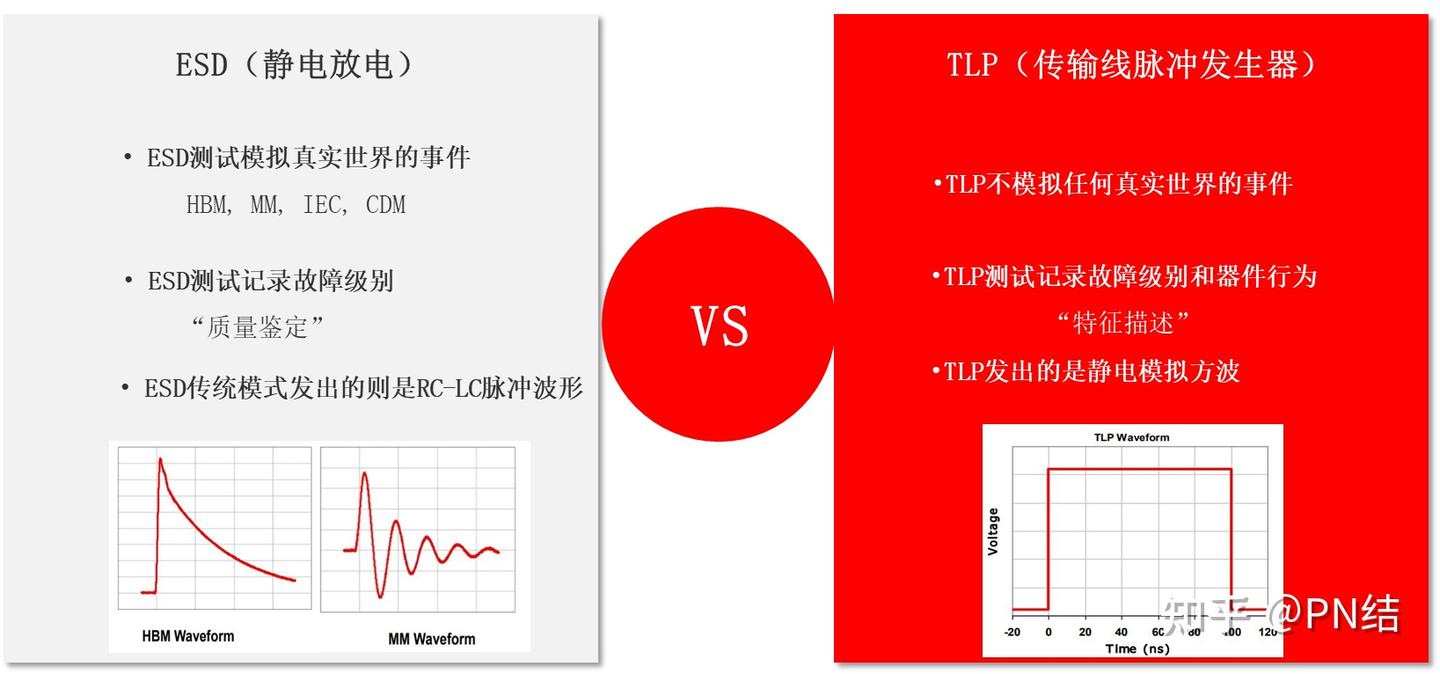

传统上,使用标准 HBM、MM 和 CDM 测试方法的常规“PASS/FAIL”ESD 测试仪测试 ESD 保护和 IC 的 ESD 鲁棒性。这些测试本身仅提供故障级别。然后使用应力后失效分析(SEM、光发射显微镜 (EMMI)、光学显微镜、LCD)来识别保护装置或 IC 中的弱点

并且随着工艺技术进入深亚微米和纳米尺度,对片上 ESD 保护设计的要求变得更加严格。非受控工艺变化可能发生在裸片内、晶圆内、晶圆与晶圆之间以及批次与批次之间,这会影响许多产品的 ESD 性能。对于IC设计人员来说,可以进行各种精确的模拟,以评估工艺变化对集成电路在不同工艺角的影响,包括TT(Typical model)、SS(Slow-Slow)、FF(Fast-Fast)等。但是,电路级 SPICE 仿真通常不适用于回弹式 ESD 保护器件.

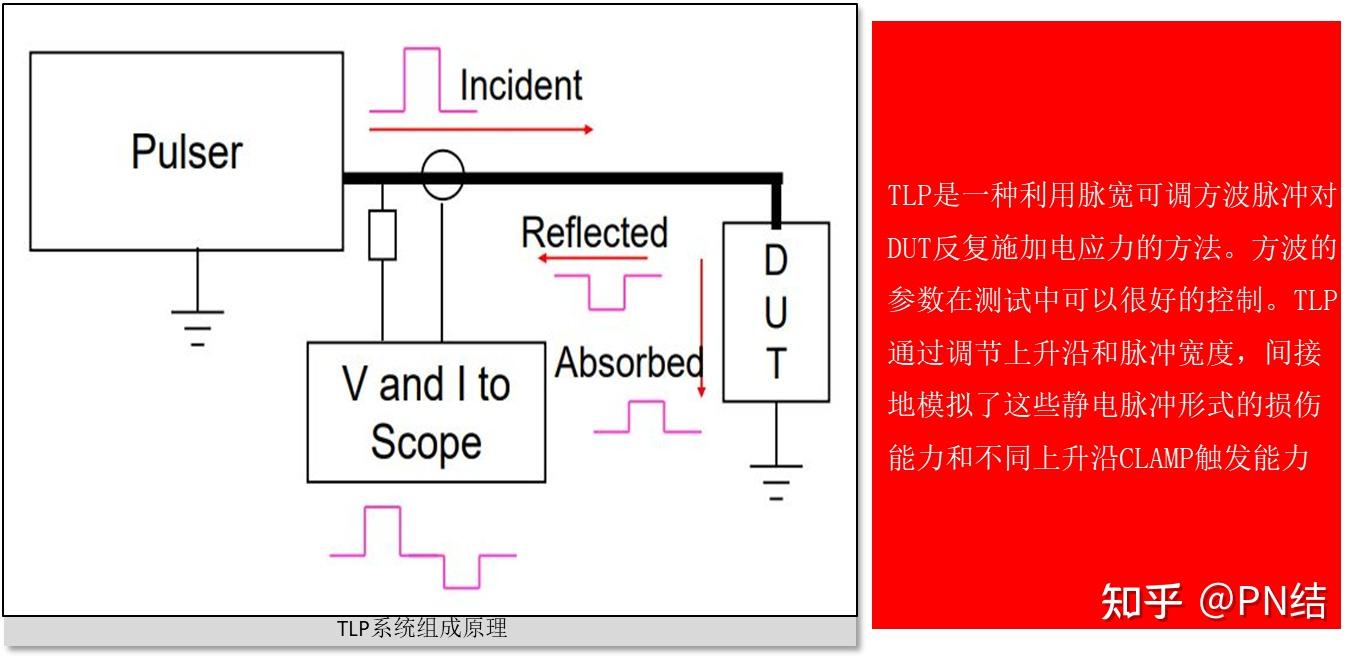

二:TLP(Transmission Line Pulse)介绍

TLP是一种利用传输线产生短脉冲来测试集成电路保护结构抗ESD能力的方法。可以用于集成电路ESD防护设计的仿真,达到集成电路ESD防护结构设计目的. 与HBM、MM等ESD测试模型相比,TLP不仅可以测量ESD的失效阈值,还可以提供详细的数据来了解元器件的失效机制。因此TLP广泛应用于ESD保护电路的设计优化

三:TLP(Transmission Line Pulse)测试原理

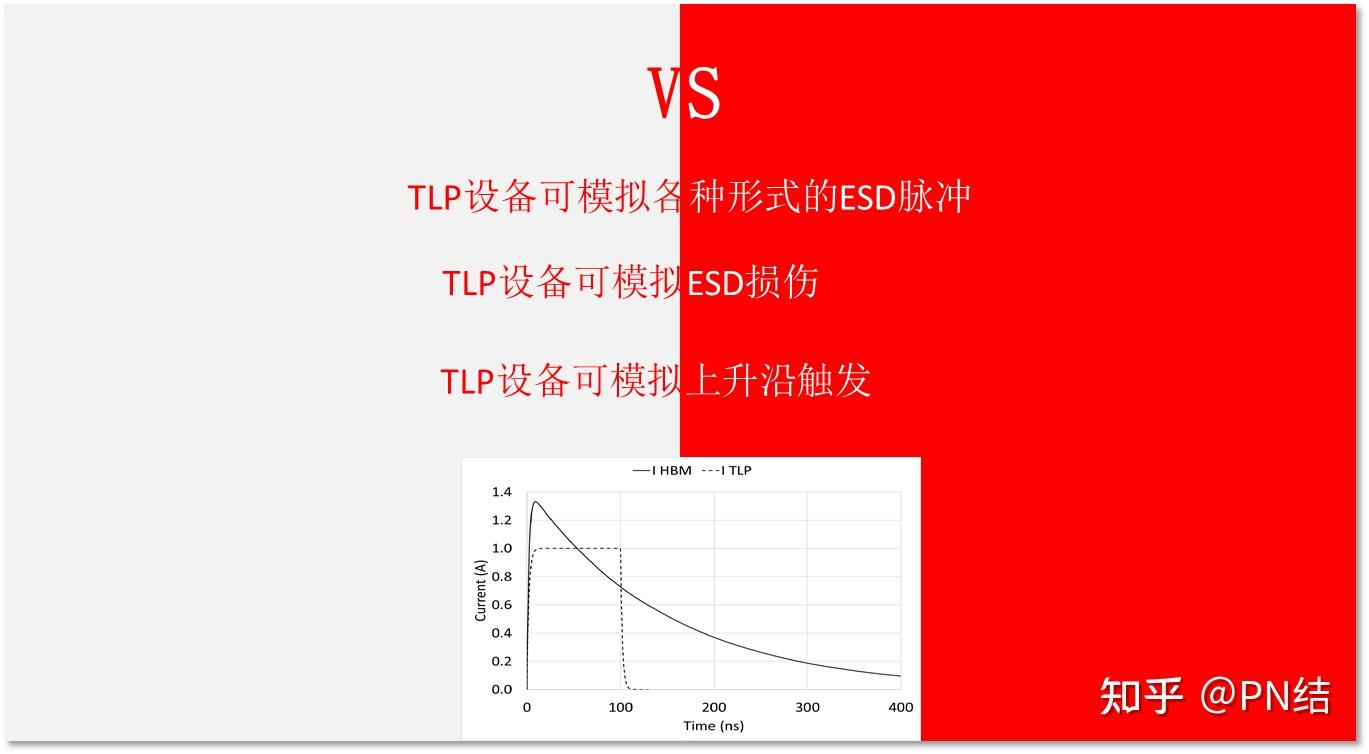

四:TLP 与 ESD的区别是什么?

五:TLP 与 ESD的相同点是什么?

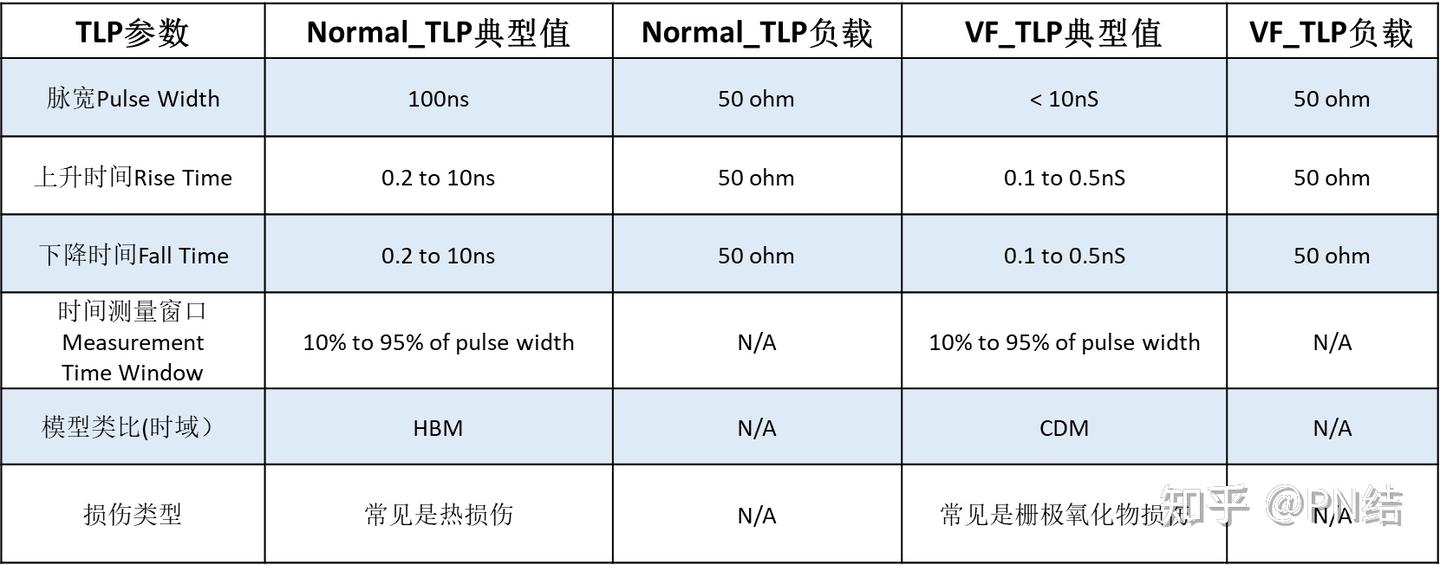

六:Normal_TLP与VF_TLP对比

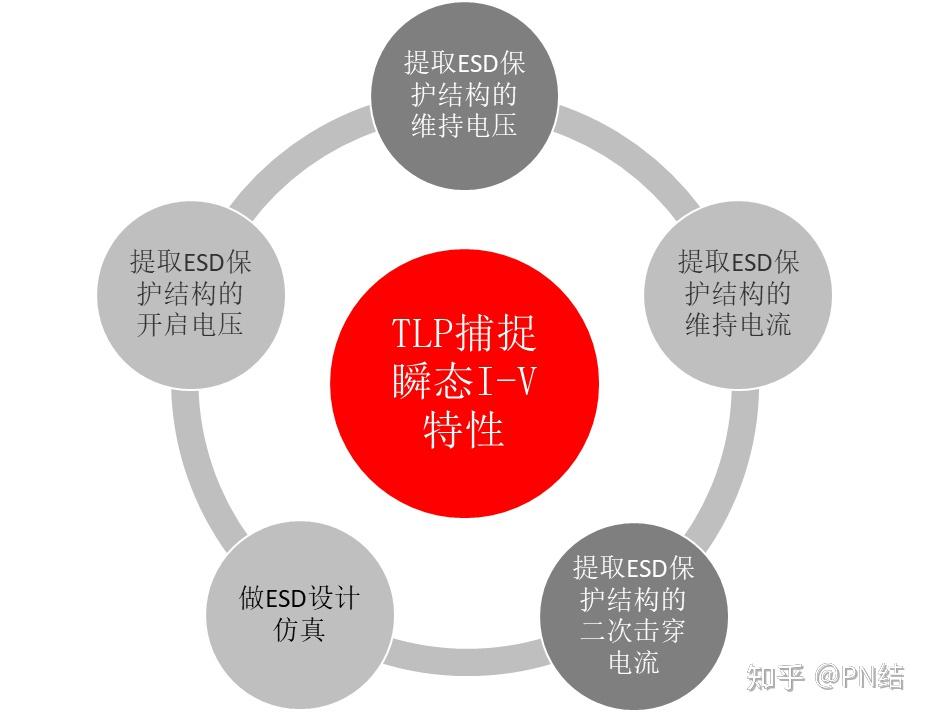

七:从TLP测试数据中我们能得到什么?

1:从 TLP 表征中收集的当前能力可用于估计结构的 HBM 等级。TLP 的最大优势是电压和电流测量,以根据类似 ESD 的应力构建 IV 特性

2:使 ESD 设计人员能够了解结构的导通位置、导通电阻、保持电压及其故障点。它还可以表征响应,例如非常适合 ESD 保护的回弹响应。传统的 S 参数或 DC 测量无法提供这种有价值的 ESD 信息

3:TLP 也已应用于完整 IC 的故障排除。虽然理想情况下,全部 ESD 电流都应该流过保护电路,但在实际 IC 中情况并非总是如此。因此,完整电路的 TLP 分析不仅会再现保护器件的 IV 特性,而且可能会显示更复杂的行为

以专业赋能行业,推动静电防护意识升级

思研科技作为静电防护整体解决方案专家,已累计为100+企业提供:

● 静电工程设计与施工

● ESD认证咨询与体系搭建

● 智能静电监控系统

● 定制化培训服务

制造企业:静电防护不容忽视,专业的事交给专业的人!期待与更多企业携手,构建更安全、更高效的生产环境。