作者:😃思研

2026-01-04

传输线脉冲测试(TLP)

传输线脉冲测试(TLP)测试是一种用于评估ESD(静电放电)保护装置的高度专业的方法。基本原理是利用脉冲电流模拟ESD事件,以测量器件在不同应力条件下的电压和电流响应。通过TLP测试,我们可以获取器件的IV(电流-电压)特性曲线,这对于理解器件的动态响应以及评估其在ESD事件下的性能至关重要。CTI华测检测可提供的一站式ESD测试方案,实验室内配有多项静电防护测试设备,满足产业客户各类静电防护测试需求。

什么是传输线脉冲测试

传输线脉冲测试(TLP)测试是一种用于评估ESD(静电放电)保护装置的高度专业的方法。

基本原理是利用脉冲电流模拟ESD事件,以测量器件在不同应力条件下的电压和电流响应,通过几P测试。我们可以获取器件的N(电流.电王)特性曲线,这对于理解器件的动态响应以及评估其在ESD事件下的性能至关重要。

传输线脉冲测试

1.优势

TLP测试的关键优勢之一是其高电流脉冲能力,与传统的ESD测试相比,TLP测试可以生成高达几安培的脉冲电流,能够提供更真实的ESD事件模拟。这种高电流脉冲更接近于实际ESD事件中的电流水平,对于评估器件在ESD事件中的真实响应至关重要。

在TLP测试中,二次击穿电流(12)是一个垂要的参数。12代表了器件能够承受的最大ESD电流。一旦ESD电流超过了12,器件就可能会损坏,从而导致永久性失效。因此,准确测量和理解12对于评估器件的ESD保护性能至关重要。

除了12之外,TLP测试还提供了其他重要的信息,例如器件的开启特性、急变返回特性和保持特性。这些信息反映了器件在ESD事件中的动态响应和稳定性,对于评估器件的全面性能至关重要。

2.TLP设备原理

3.TLP设备

4.TLP设备规格

Thermo ScientificTM Celestron

Pulse voltage: OV-2000v,in 0.2V/step

Pulse current: Maximum 40A

Pulse width: Fixed at 100nsec

Pulse rise time: 10nsec

Leakage measurement: 50 pA

所有半导体集成电路 (IC) 在其整个生命周期都会受到环境静电放电 (ESD) 的影响。设计师利用多种技术保护这些敏感的电子部件免受意外 ESD 事件造成的损坏。行业采用标准化的ESD半导体鉴定方法,根据一套定义明确的应力标准对部件进行鉴定,从而产生分类,然后针对单个部件指定分类。这些分类表明部件在没有任何潜在或灾难性故障的情况下可以承受的最大应力。

每个 ESD 控制计划都必须识别产品组合中对 ESD 敏感的器件。为此,您需要对其灵敏度进行分类。产品对 ESD 损伤的敏感性取决于其以下能力:

- 释放放电能量

- 承受电流水平

过去,基于三种不同 ESD 模型的主要分类有三种:

| 模型 | 等效电路 | 标准 |

|---|---|---|

| 人体模型 (HBM) | 100 pF (1.5 kΩ) | ANSI/ESDA/JEDEC JS-001 |

| 带电器件模型 (CDM) | 6.8 pF/55 pF 模块 | ANSI/ESDA/JEDEC JS-002 |

| 机器模型 (MM) | 200 pF (0 Ω) | ESD STM5.2/JEDEC JESD22A115 |

最近,MM 被取消为标准测试方法,使 HBM 和 CDM 成为目前仅有的 ESD 模型。

人体模型

ESD半导体鉴定部件的最常见模型为 HBM。该模型模拟人(例如手或手指)与导体(例如金属轨)之间发生的放电。对于该模型,100 pF 电容器通过 1,500 Ω 电阻器放电,以模拟人体产生的波形。通过短路导线的电流脉冲 (ESD) 的典型上升时间平均为 6 ns (6 x 10-9 s),并且对于较高的电阻负载而言较慢。对于 1000 V 预充电,通过短路的峰值电流平均为 0.67A。

ESD鉴定期间指定给部件的分类基于部件能够在无损坏(潜在或灾难性)的情况下承受的最大电压应力。下表符合 ANSI/ESDA/JEDEC JS-001:

| 类别 | 电压范围 |

|---|---|

| 0Z 级 | < 50 V |

| 0A 级 | 50 V 至 < 125 V |

| 0B 级 | 125 V 至 < 250 V |

| 1A 级 | 250 V 至 < 500 V |

| 1B 级 | 500 V 至 < 1000 V |

| 1C 级 | 1000 V 至 < 2000 V |

| 2 级 | 2000 V 至 < 4000 V |

| 3A 级 | 4000 V 至 < 8000 V |

| 3B 级 | ≥ 8000 V |

带电器件模型

在 CDM 模型中,是器件本身带电;这通常通过滑出管/袋/分拣机等产生摩擦引起。当带电部件以不同的电位接触导体(例如桌面、手或金属工具)时,器件将迅速放电至该导体,并可能导致后续器件故障。放电时间可能非常短(小于 1 纳秒),但峰值电流可能非常高。CDM 模型使用 6.8 pF 或 55 pF 验证模块(硬币),模拟 2 至 30 安培的峰值电流。下表符合 ANSI/ESDA/JEDEC JS-002:

| 类别 | 电压范围 |

|---|---|

| C0a 级 | < 125 V |

| C0b 级 | 125 V 至 < 250 V |

| C1 级 | 250 V 至 < 500 V |

| C2a 级 | 500 V 至 < 750 V |

| C2b 级 | 750 V 至 < 1000 V |

| C3 级 | ≥ 1000 V* |

* 不建议在 1000 V 以上进行测试,参见标准注释 3。

标准委员会强烈建议使用 HBM 和 CDM 对每个半导体组件进行全面分类。这意味着一个项目可以分为 2 级 (HBM) 和 C1 级 (CDM)。这些半导体鉴定指南通常用于:

- 开发和测量合适的芯片上保护

- 实现器件(竞争性)之间的比较

- 提供 ESD 灵敏度分类系统,以协助满足生产和装配环境的 ESD 设计和监控要求

- 拥有记录测试程序,以确保可靠和可重复的结果

请参见我们产品页中的一整套ESD半导体测试系统,帮助满足您的器件鉴定要求。

通过HBM、MM、CDM测试只能得到一个器件的失效电压,如果要进行ESD防护器件的研究和性能的优化,还需要获得更多的电学信息。ESD防护器件设计的安全裕量是由器件的敏感性决定的,考虑到在大多数的先进制程和应用中,安全裕量是变化波动的,因此在ESD事件发生时,对防护器件的各种电学参数的准确测量至关重要。由于直流特性在大电流时会产生严重的自加热效应,并不能表征ESD事件发生时的瞬态特性,所以传输线脉冲(TLP)测试技术就变得十分必要了。

TLP测试技术最早由Maloney和Khuranal在1985年引入的,用于研究集成电路器件在ESD事件发生时电压和电流在时域上的关系。目前TLP测试已经成为ESD防护设计中必不可少的手段。

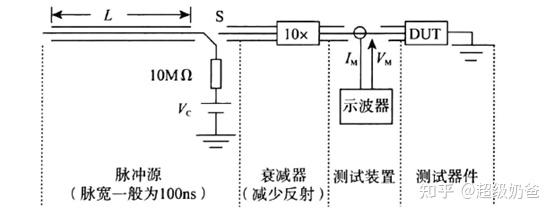

TLP测试系统的组成原理图如图1所示,由脉冲源、衰减器、测试装置和测试器件(DUT)四部分组成。

根据脉冲产生方式的不同,TLP系统可以分为时域反射(Time Domain Reflection,TDR)、时域传输(Time Domain Transmission,TDT)、时域反射和传输(Time Domain Reflection and Transmission,TDRT)和电流源(Current Source)

(500Q阻抗)四种方式,其中TDR又可分为TDR-O和TDR-S。这里介绍的TLP测试系统Barth 4002是一种TDR-O系统,在测试过程中所得的曲线通过传输线的入射波和反射波叠加而成,测得的初始数据为瞬态脉冲下电压-电流关于时间的特性。

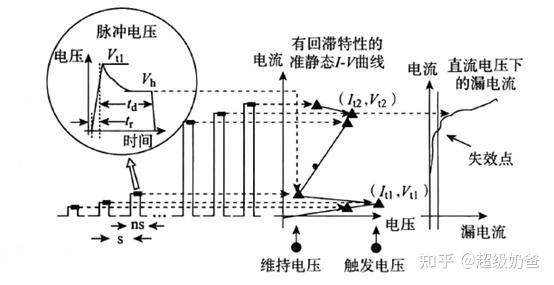

Barth 4002 TLP系统产生的一系列短暂的脉冲方波是根据HBM的能量等效原则生成的,如图2所示。

脉冲波形与直流波形的最大不同就是脉冲波形是离散的,能更好地模拟ESD冲击的瞬态特征。每个脉冲波形的上升沿时间约为10ns,脉宽约为100ns,用以模拟和HBM波形相近的能量脉神的幅度根据预先设置的步长逐步递进。在每发出一个脉冲波形后,对器件作一次直流漏电流测试,所施加的电压也是预先设定的。正常情况下,器件的漏电流非常小,约为 A级。当某一次脉冲波形过后测得的漏电流值突然增大(一般增大3个数量级)时,说明器件已经损坏,脉冲波形停止传输。

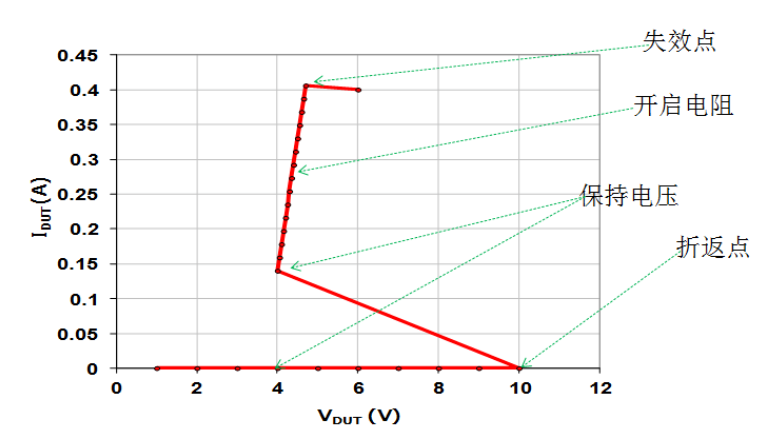

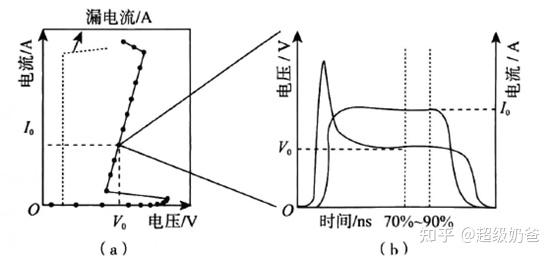

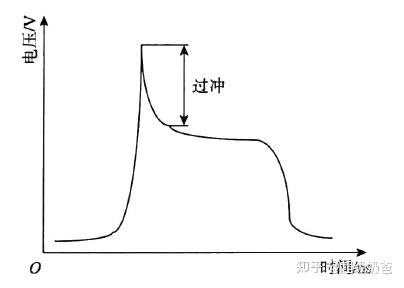

图3所示为具有snapback特性的ESD防护器件的典型TLP测试曲线,横坐标为电压,纵坐标为电流。每一个测试点对应的漏电流值也绘制于同一幅图中。其中每一个测试点的绘制方法如下:TLP测试系统的脉冲源每发出一个脉冲,测量装置就测试DUT端的电压和电流关于时间的波形。由于波形反射叠加等因素,测得的电压-电流波形已不再是规则的方波,而有可能是如图3(a)所示的波形。

然后分别取整个测量周期70%~90%时间段内的电压、电流平均值,形成一个坐标点,绘制于TLP测试图中。

在TLP测试获得的电压-时间波形中,还能反映出一个表征ESD防护器件性能的关键指标:开启速度。电压波形上存在一个尖峰(如图4所示),称为过冲(overshoot)。一般来说,如果防护器件开启速度快,那么过冲就小。如果一个防护器件的开启速度过慢,那么即使在TLP测试曲线上反映出来的开启电压很低,在实际的ESD冲击下,由于防护器件不能及时开启提供ESD电流泄放通路,也会使被保护对象被过高的过冲损坏。因此在进行ESD防护设计时,开启速度也是必须考虑的一个因素。

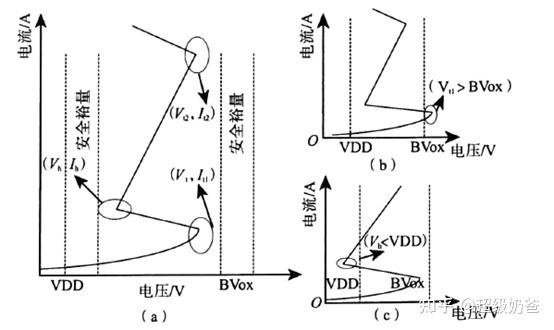

在ESD设计中,ESD设计窗口(ESD design window)是一个重要的概念,如图5所示。

图5(a)中绘制了一条具有snapback特性的曲线。常用的ESD防护器件除了二极管外,一般都有回滞特性。图中标示出了三个用来表征ESD防护器件性能的关键参数:开启电压(也称触发电压(Vt1)、维持电压(Vh)、二次击穿电流(It2)。此外还标示出了被保护电路的工作电压(VDD)和击穿电压(BVox)。

作为ESD防护器件,最关键的一点就是在ESD事件发生时,能钳住电压,使其不高于BVox。Vt1表示防护器件在开始工作初期所达到的最高电压,之后由于新的导通路径形成,会有一段负阻区形成,也就是防护器件两端电压减小而流过的电流增大的过程。因此,设计时为了发挥防护器件的有效性,必须让Vt1小于BVox。一般在设计实践中,Vt1是一个需要设法降低的值。当ESD防护器件的新导通路径完全形成后,就会保持一个相对稳定的阻值。在曲线上就表现为负阻区结束,曲线又进入电压、电流双双递增的区域,该递增曲线的斜率就反映了防护器件本身的阻值大小。从负阻区到递增区之间的转折点电压用Vh表示(有时也用Vsp表示)。为了保证ESD防护器件的透明性,即电路正常工作时,ESD防护器件不会开启,并且为了避免门锁效应的发生,Vh必须高于VDD。在设计实践中,Vh一般是一个需要设法提高的值。ESD防护器件泄放电流有一个最大值It2,即二次击穿电流,超过这个值,ESD防护器件自身就会因发生不可恢复的热击穿而失效。在设计实践中,总是设法提高防护器件的It2。

考虑到实际情况与理论的一些偏差以及芯片工作电压的波动等因素,就需要考虑一定的安全裕量。也就是说,防护器件的I-V曲线上的电压下限一般根据实际需求比VDD高10%~20%,必须高于这个值;电压上限比BVox低10%~20%,以避免过压(overshoot)的瞬态冲击,所以Vt1必须低于这个值。在实际的ESD防护设计中,根据被保护芯片的具体参数VDD和BVox设定好安全裕量,然后在这个ESD设计窗口中设计出具有高Vh低Vt1,的防护器件。图5(b)和图5(c)分别给出了开启电压超过击穿电压、维持电压小于工作电压的例子,这些当然是不满足正确设计要求的情况。

如今随着工艺的进步,ESD防护器件设计的难度也可以从ESD设计窗口得到很好的体现:由于氧化绝缘层变薄,击穿电压BVox降低的趋势往往快于工作电压VDD降低的趋势,导致ESD设计窗口越来越窄,因而对Vh、V1的设计要求也越来越苛刻。

以专业赋能行业,推动静电防护意识升级

思研科技作为静电防护整体解决方案专家,已累计为100+企业提供:

● 静电工程设计与施工

● ESD认证咨询与体系搭建

● 智能静电监控系统

● 定制化培训服务

制造企业:静电防护不容忽视,专业的事交给专业的人!期待与更多企业携手,构建更安全、更高效的生产环境。